DAQ-121 – High-Speed Digitizer

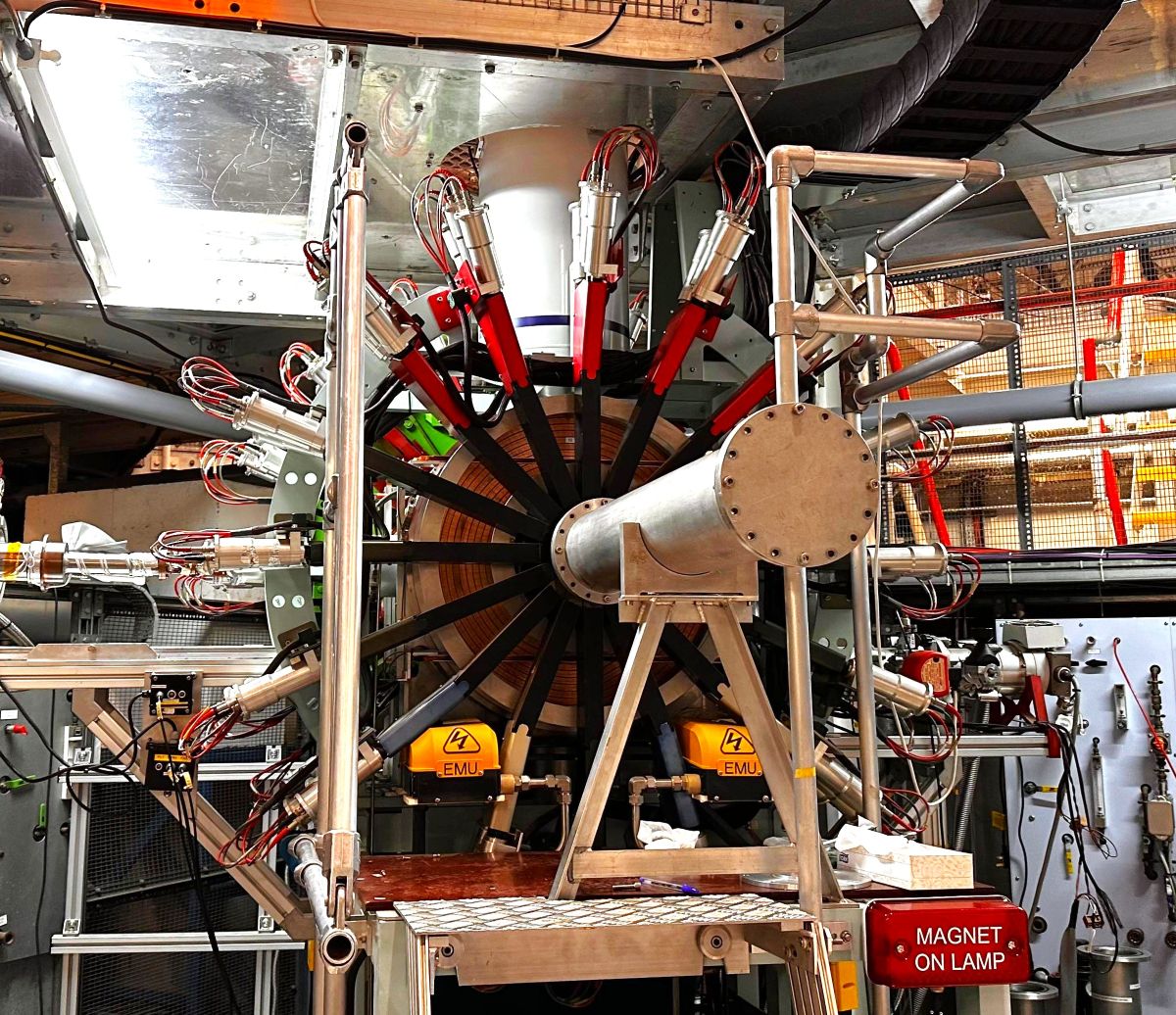

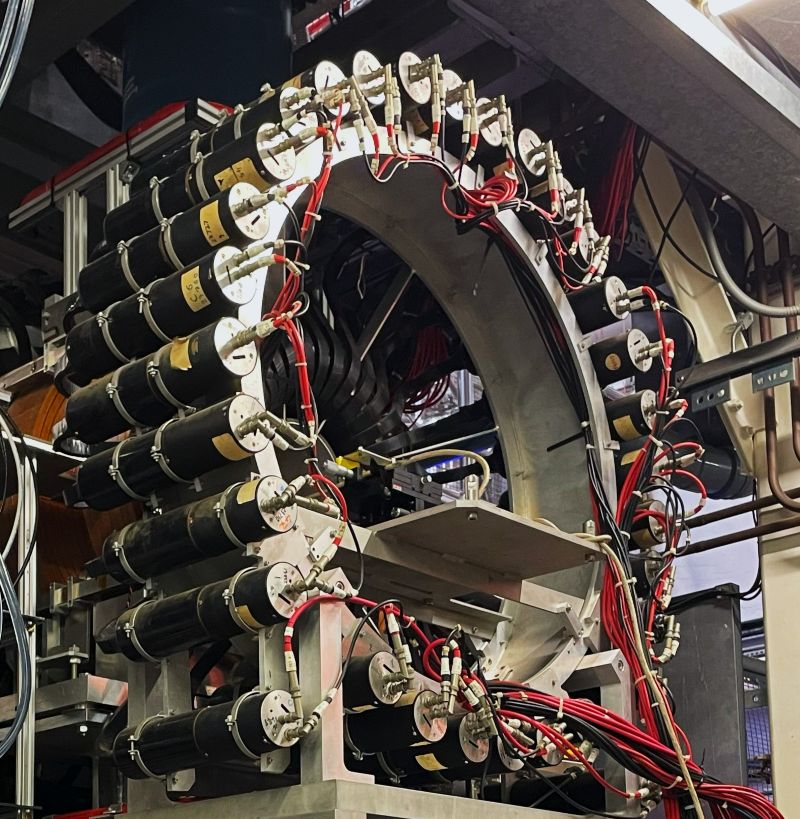

The DAQ-121 is a high-performance, fully integrated digitizer developed by Nuclear Instruments for advanced SiPM-based muon detection systems. Designed to operate in demanding scientific environments, such as the ISIS Muon Facility, the DAQ-121 provides real-time digitization, processing, and streaming of high-speed analog signals from up to 32 channels simultaneously.

Key Features

- Compatible with Sci-Compiler for easy integration and development

- 32 independent analog input channels

- 12-bit ADC @ 1 GSPS per channel

- 2 GHz analog bandwidth

- Fully differential RJ45 analog inputs

- Real-time signal processing and data reduction

- Embedded Linux system on Zynq Ultrascale+ SoC

- 4× ARM 64-bit cores per module + Kintex-7 master FPGA

- Integrated power and bias control for SiPM detectors

- High-speed data streaming via Kafka and ZeroMQ

- EPICS & IBEX integration

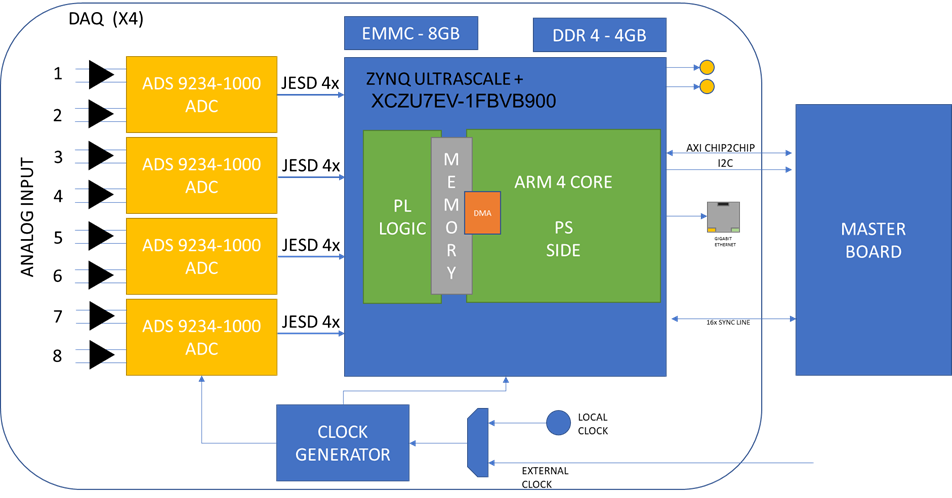

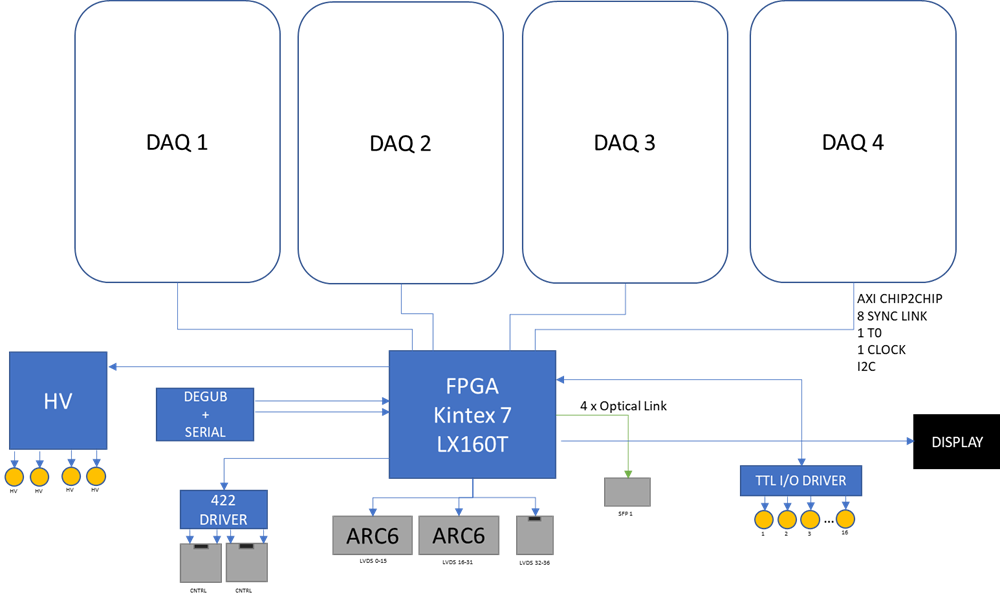

System Architecture

Each DAQ-121 module integrates:

- 4 DAQ boards, each handling 8 channels and controlled by a Zynq Ultrascale+ SoM

- 1 master Kintex-7 FPGA aggregating and routing data

- 4× SFP optical transceivers for future optical data links

- 1 Gbps Ethernet link per board for data and control

- Integrated display for IP and voltage monitoring

- Multiple synchronization and I/O interfaces (TTL LEMO, LVDS, RJ45)

Block Diagram of the DAQ-121 system architecture. Each module integrates 4 DAQ boards, each handling 8 channels and controlled by a Zynq Ultrascale+ SoM.

Block Diagram of the DAQ-121 system architecture. Each module integrates 4 DAQ boards, each handling 8 channels and controlled by a Zynq Ultrascale+ SoM.

Signal Acquisition & Processing

- Digitizer mode: waveform acquisition on trigger (external/internal/periodic) with pre-trigger buffer up to 4 µs and post-trigger up to 120 µs

- PHA mode: real-time multichannel spectrum analysis between acquisition cycles

- Processing algorithms: exponential deconvolution, peak detection, digital CFD, timestamp extraction

- Max processed event rate: >10 MHz per channel

Calibration & SiPM Monitoring

- Real-time SiPM dark count spectrum analysis via embedded derivative trigger and QDC core

- Photon quantization and spectrum per channel

- Active gain stabilization via digital feedback and programmable bias control

- Remote access to per-channel temperature, bias, and heater status

Interfaces and Integration

- 24 TTL LEMO I/O (configurable)

- 32-channel LVDS sync connector

- Clock & trigger over LEMO or LVDS

- Integrated T0 and status packet receiver (ISIS-compliant)

- EPICS/IBEX-ready control and readout

- Kafka-ready data streaming

- Python SDK + C++ BSP + VHDL firmware (open)

Performance Summary

| Parameter | Value |

|---|---|

| ADC resolution | 12 bits |

| Sampling rate | 1 GSPS per channel |

| Analog bandwidth | 2 GHz |

| Input impedance | 100 Ω differential |

| Pre-trigger buffer | up to 4 µs |

| Post-trigger buffer | up to 120 µs |

| Energy spectrum resolution | up to 4096 bins |

| Min integration time | 4 ns |

| Max integration time | 40 µs (digitizer), 360 s (spectrum) |

| Output formats | Waveform or processed list |

| Output protocols | Kafka, ZeroMQ |

| Control protocols | ZeroMQ, EPICS |

| Power consumption | ~800 W |

| Input voltage | 115–240 V AC |

SiPM Bias and Power Control

- Bias range: 20–80 V

- Max current: 10 mA per channel

- Bias noise: <300 µV RMS

- Stability: 4 mV/°C

- 4 independent staves supported, each with ±6 V regulated power and RS232 interface

Applications

- Muon spin rotation and relaxation (μSR)

- Time-resolved spectroscopy

- Neutron and gamma detection with SiPMs

- Custom detector readout in high-rate environments