Description

The DT5550W is a reliable prototyping DAQ platform designed to readout Analog and Digital ASICs. The full system is composed by two boards:

- Base board with an FPGA, usb 3 connectivity, power supply, ADCs, power supply

- ASIC daughter cards that host ASICs, detectors (or detector connectors) and high voltage power supply.

A5550P WEEROC PETIROC EVALUATION DOUGHTER BOARD

The board is deisgned to evaluate the characteristics of WeeROC Petiroc 2 Asic and develop ready-to-use experimental System. The board firmware and software is distributed open-source and can programmable by the Nuclear Instruments SCICompiler Development Studio.

DT5550W FEATURES

- More then 200 digital channels

- 10mA Output Current

- 8 analog acquisition channels, 80 Msps 14 bit to monitor ASIC outputs

- Programmable low jitter (less then 1ps) clock source as reference for on chip TDC

- SPI and I2C controller for ASIC configuration

- USB3 bus

- 8 I/O CMOS digital connector for external synchronization

- SCICompiler Graphical software tool for the automatic generation of firmware and C++ libraries

A5550P FEATURES

- Up to four WeeRoc Petiroc 2 ASICs support

- Up to two Hamamatsu S13361-3050NE-08 MPPC 64 channels Matrix

- Integrated HV Power Supply (NIPM12) for detector biasing. HV module can be controlled and monitord from USB bus

- Ultra low noise power supply. Less than 100uVpp ripple on PetiROC rails

- Possibility to provide external Bias to the detector

- Avaibility of detector extension cable (Samtec Micro-Coaxial cables) to remote the detectors

- 3D Printed Dark Room with FC coupling connector

- Supported by SCICompiler to create in few minute a full readout system

- Supported by Open source example readout system: SCICompiler project, VHDL, bitstream, .NET cource code for the readout GUI

A5550P FUNCTIONAL DIAGRAM

the PetiRoc development board A5550P hosts up to 4 Petiroc chips offering to the user the possibility to readout 128 SiPM detectors. The SiPM connectors fully matched with Hamamatsu S13361-3050NE-08 MPPC 64 channels Matrix. On the board, can be connected up to 2 matrices with the possibility to use an extension cable to arrange the two detectors in several geometry. The architecture of the digitizer DT5550W is designed to adapt, in a simple and intuitive way, the hardware acquisition architecture to the user configuration: more then 200 digital signals interconnect the mezzanine ASIC boards with the DT5550W in order to have the possibility to readout and monitor all signal from the ASICs with the FPGA. The DT5550W has an onboard 8 channels 80MSPS/14-bit simultaneous sampling ADC to monitor analog outputs from the chip. The A5550P board hosts up to 4 Petiroc chips offering to the user the possibility to readout 128 SiPM detectors. The SiPM connectors fully matched with Hamamatsu S13361-3050NE-08 MPPC 64 channels Matrix. On the board, can be connected up to 2 matrices with the possibility to use an extension cable to arrange the two detectors in several geometry. The board is fit with HV module to power both SiPM matrices (regulable voltage between 20 and 85V). The board routes all Petiroc pins to a 400 pin mezzanine connector. The board distribute the clock to all petiroc minimizing the jitter. It also generates all ASIC power supply using ultra low noise linear regulator

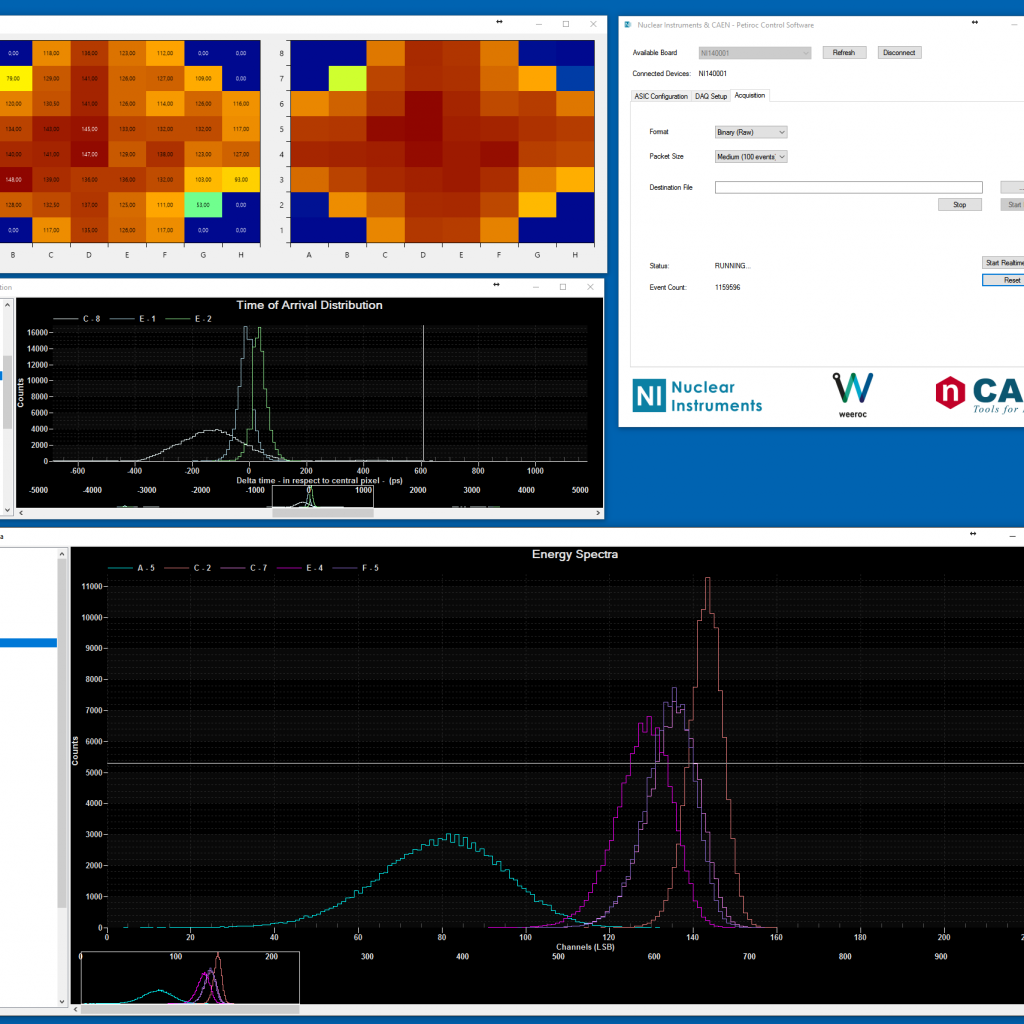

PETIROC READOUT SOFTWARE

The Windows software is available for free and distributed in open source format. The software is written in VB.NET 2015 and it is very easy to costumize.

The software is able to configure and readout two PetiROC ASICs.

The intuitive GUI allows the user to:

- Configure the two PetiROC chip

- Dump on file all data in output of PetiROC ASIC in binary format or decoded in easy-to-read JSON format

- Execute realtime plot of:

- Image View both in single frame shot and cumulative image

- Energy Spectrum for each channels

- Time distribution in respect of one channels (assumed as T0)

This product is sold with CAEN