Description

The DT5550 is a 32 channels digitizer that integrates an open FPGA that can be programmed by the user to implement most common readout features like: a sequencer to handle the readout of both analog and digital front end ASIC; complex trigger logic, pulse height analysis and time tagging feature to readout multi-channel detectors (for example SiPM matrix). The readout system is based on 32 14-bit 80 MS/s ADCs, used to sample up to 32 analog inputs. The data acquired by the ADCs is then forwarded to an FPGA that can be configured by the user through a graphical developing platform (SCI-Compiler) and used as the sequencer for the system readout. The DT5550 also integrates a reconfigurable area where it is possible to implement trigger logic, external circuit management, and real time signal processing (like trapezoidal filers, charge integrator, baseline compensation, time to digital converters, etc.). To facilitate the development process, a graphical software automatically generates the VHDL source code and C libraries, with no need for the user to learn VHDL or Verilog to configure the board. The generated code is still available to the user that can customize it as needed. To make easy for the user the development of a custom firmware, a license of SCI-Compiler softwareis included in the product.

FEATURES

- Integrated system for the management of ASICs with multiplexed analog output and multi-channel detectors

- 32 analog input acquisition channels (fully differential, 2 Vpp dynamic range)

- 80 MS/s 14-bit ADC

- 96 digital (48 differential) I/O on VHDCI connector with selectable 3.3V, 1.8V CMOS or LVDS for the sequencer and the management of external circuits

- 8 digital CMOS I/O on LEMO connector for external synchronization

- 8 dedicated I/O for UART/I2C/SPI

- Standard high density VHDCI I/O and analog connector:

- 1 analog connector with 32 analog channels and a I2C bus

- 2 digital connectors with 48 digital channels (each) and programmable power supply

- Fully supported by SCI-Compiler, graphical programmable compiler for user application development (INCLUDED)

- 0 ÷ 5.5V 2A power supply

- 12V powered

- User firmware can be designed to easy implement most common readout system feature:

- Readout of both analog and digital front-end ASIC with user customizable pre-processing logic like zero suppression, pedestal subtraction

- Multichannel analyser based on both trapezoidal filter or charge integration with user customizable filtering chain

- Time to digital conversion and time tagging application

- Digitalization of waveforms

- Complex triggering logic involving both analog and digital processing

- USB3.0 bus for fast data transfer, integrated SPI master core and I2C/UART core

STANDARD FIRMWARE

The DT5550 system is a fully programmable readout system. Processing algorithms and readout system can be developed with SCICompiler.

By the way, Nuclear Instruments provides the following fully working firmwares and softwares ready to use to implement standard readout system

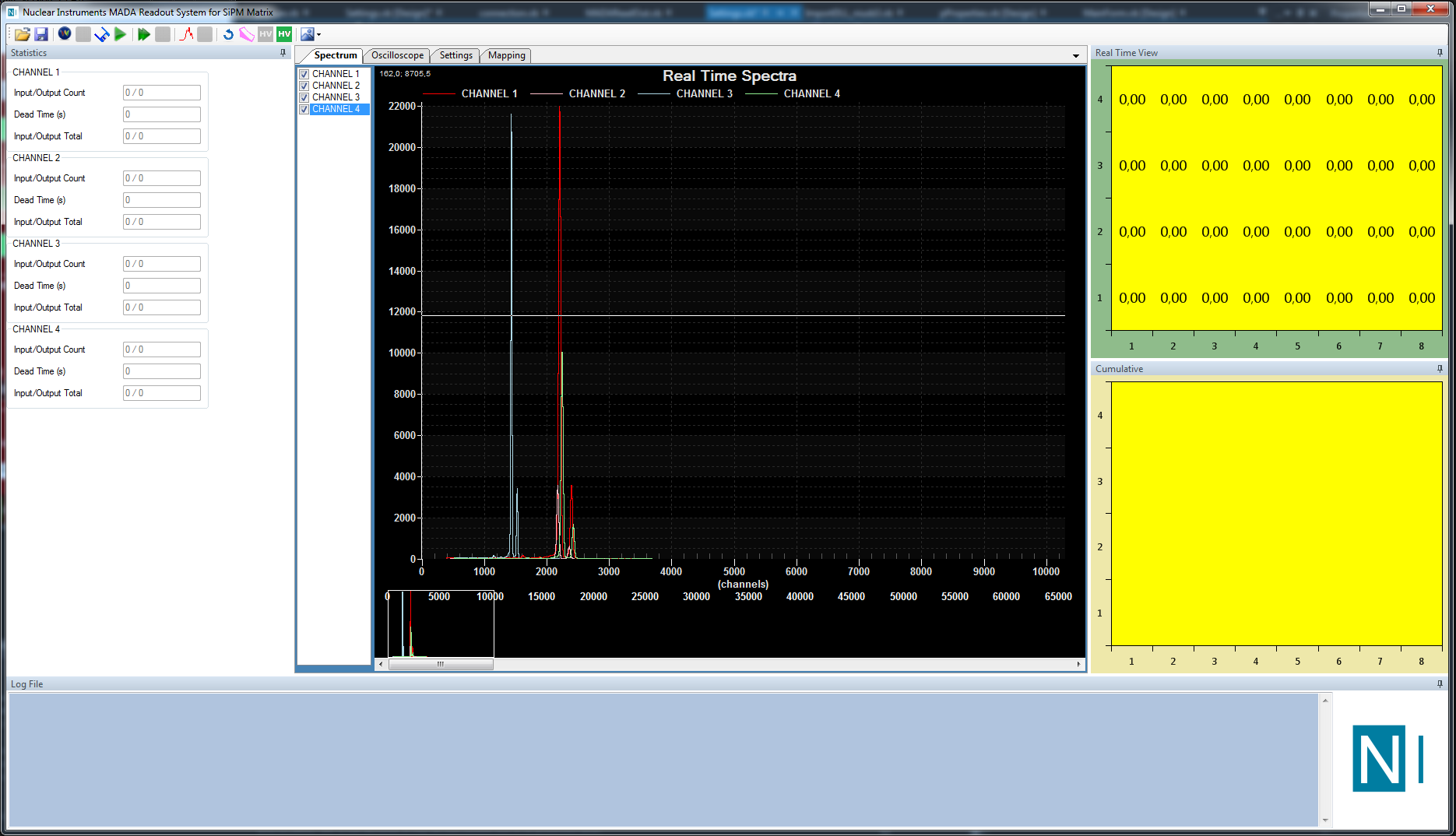

- MCA for HPGE, PMT and Silicon detector:

- 32 input channels

- 32k channels spectrum

- Less then 0.05% intrinsic resolution

- Up to 2 MCPS

- Trapezoidal or Charge integration

- Baseline restorer with programmable length

- Programmable length pileup rejector

- Derivative and leading edge trigger

- Integrated Oscilloscope on all 32 channels

- Indipendent digital VETO on all 32 channels

- Full working open source windows software with oscilloscope and spectrum functionalities

- Fitting tool on spectrum data

- Energy Calibration

- Imaging software module for spatial detector

- Waveform Digitizer

- 32 input channels

- 32k sample per channel

- Derivative and leading edge internal trigger

- External trigger

- Programmable delay on input trigger

- Indipendent digital VETO on all 32 channels

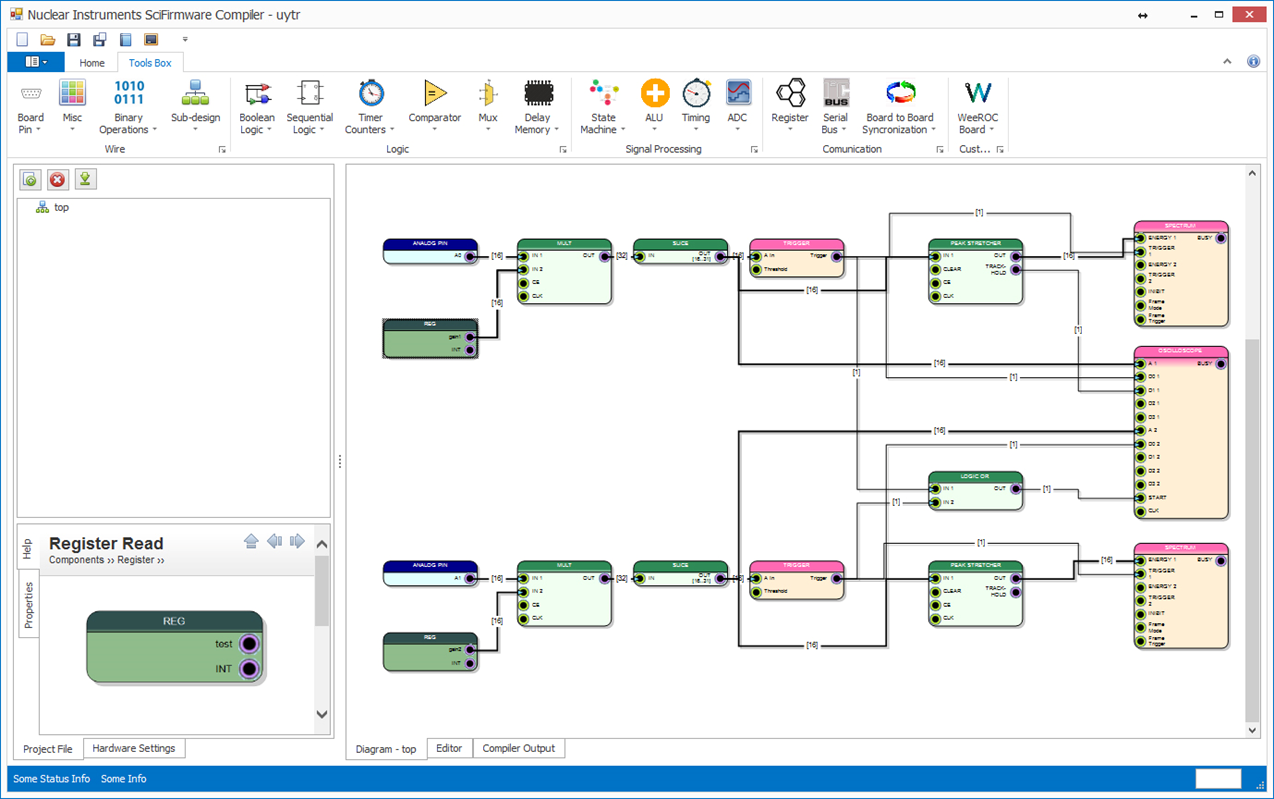

SCI-COMPILER

DT5550 includes the SCI-Compiler software, a graphic tool which allows the user to realize a whole readout logic for ASICs and detector unit connected to the module. The software generates the VHDL source code, C libraries, drivers and a C example code (to be compiled on Windows or Linux) to help integrating firmware vs software automatically without requiring to be a VHDL expert.

This product is sold with CAEN